Wszystko

Najnowsze

Archiwum

źródło: temp_file.png3447172087652299467

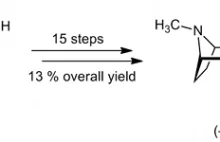

PobierzGdzie najlepiej i najwygodniej robić siku?

- Do butelki 2.8% (1)

- Do blaszanego wiaderka w kącie pokoju 5.6% (2)

- Pod blokiem 13.9% (5)

- Do umywalki 19.4% (7)

- Do nocnika 5.6% (2)

- Do kwiatów doniczkowych 13.9% (5)

- Na klatce schodowej 0% (0)

- Koledze na buzię 8.3% (3)

- Pod siedzibą PIS 11.1% (4)

- W pieluszkę :3 19.4% (7)

Komentarz usunięty przez moderatora

- 21

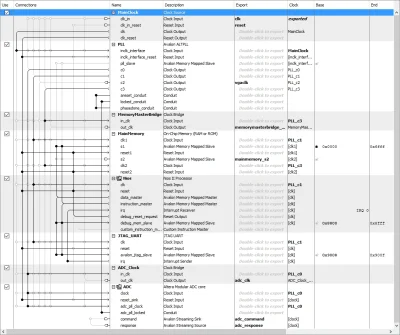

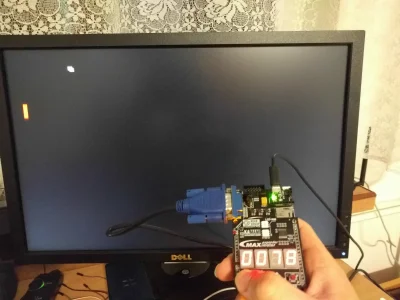

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

źródło: comment_yKlgVPc8UOU7D9ZREo85MjJeETRcFpTB.jpg

Pobierz- 27

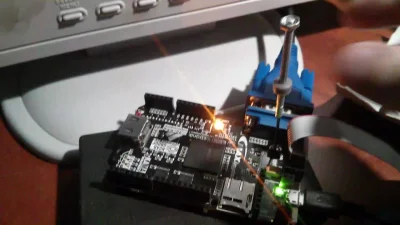

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

źródło: comment_YX1P0z92fKFIu29AN2sOiZcdHCEHN66T.jpg

Pobierz- 1

- 1

- 14

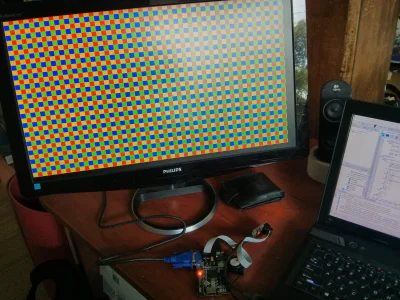

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

źródło: comment_ljITNk4VBphsl5BDIF9Wvfzf2G1Q8j4v.jpg

Pobierz- 7

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

źródło: comment_Uttil5ouGIUCZP1dJIAxofc3OqMllhy7.jpg

Pobierz- 1

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

- 1

- 8

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

źródło: comment_WDOwVE0BJ7UQVWtuR68VNtf4y3YOvDg6.jpg

Pobierz- 13

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

źródło: comment_KloDqPjcmjE27kpVgI9EuTbCQS4ovtXF.jpg

Pobierz- 1

- 0

- 2

Q <= '1' when (clkCounter = target) else '0';Kod wygląda tak:

http://pastebin.com/UzSgSGPi

- 9

Na zdjęciu Pong jednoosobowy, w którym zasady są zmyślone i punkty nie mają znaczenia :)

#fpga #verilog

i #nieprogramowanie bo to #synteza ;)

źródło: comment_gmmOFk8ZqOb2VAS6aZLHlwiwl4Bv5QKk.jpg

Pobierz- 3

Polecam filmik od Ben Hecka.

230

Wszystko o Syntezie Termojądrowej

Dla osób lubiących czasopisma popularnonaukowe i interesujących się syntezą termojądrową i ogólnie energią atomową - pdf z bardzo fajnie opracowanym tematem, pisane rzeczowo ale na tyle łopatologicznie że nie trzeba być "rocket scientist" żeby zrozumieć :) Z mojej perspektywy wyczerpuje...

z- 22

- #

- #

- #

- #

- #

10

Synteza fluoresceiny...

... jednej z najbardziej znanych fluoryzujących substancji.

z- 0

- #

- #

- #

- #

- #

- #

- #

- #

23

B---a atomowa - jak to działa?

Na krótko przed wybuchem II wojny światowej, Einstein napisał list do prezydenta Roosvelta, w którym wraz z kilku innymi naukowcami zawiadomił go o podjętych w Hitlerowskich Niemczech pracach nad otrzymaniem wzbogaconego U-235, mogącego posłużyć do zbudowania b---y atomowej. I tak to się zaczęło...

z- 7

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

17

Jak tłumaczono proces syntezy białek w czasach przed wszechobecnymi animacjami?

Jak przystało na rok 1971 w iście hippisowskim stylu.

z- 0

- #

- #

- #

- #

- #

- #

34

Naukowcy z Iranu i USA chcą współpracować przy syntezie termonuklearnej [ang]

![Naukowcy z Iranu i USA chcą współpracować przy syntezie termonuklearnej [ang]](https://wykop.pl/cdn/c3397993/link_rJeGPiQbgYDaoKH7ZnHICQUricFNjGYd,w220h142.jpg)

Lawrenceville Plasma Physics Inc z NJ oraz Tehran’s Islamic Azad University rozwijają metodę, na którą ma być stać państwa uprzemysłowione. 2 m-ce temu LPP pobiło rekord temp. utrzymania plazmy: 1.8 mld st. C. Zamiast neutronów (jak w innych projektach) wykorzystują jony - nie potrzeba więc turbin.

z- 1

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

10

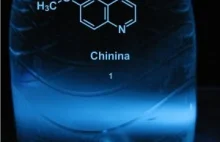

O historii syntezy chininy słów kilka

Była wojna, aliantom odciętym przez niedobrych Japończyków od bogatych w korę chinowca (i w konsekwencji – chininę) Holenderskich Indii Wschodnich (od 1949 roku – Indonezja) było ciężko. Potrzebny był spektakularny sukces propagandowy...

z- 0

- #

- #

- #

- #

- #

- #

- #

29

K-----a z cukru?

ściślej - z rybozy

z- 15

- #

- #

- #

- #

- #

- #

- #

Człowiek z reguły myśli, że "on" decyduje

źródło: unnamed

PobierzMało tego - autor podaje na wstępie informację, że to co opisuje to "model", po czym rozwija temat w sposób nie pozostawiający miejsca na interpretację, nie wchodzi w polemikę z czytelnikami (ba! Nawet usuwa komentarze - ciekawe jak