Ktoś tu jeszcze programuje w #vhdl lub #verilog czy umarło?

#programista15k #programista25k #programista30k #programista50k #programista0k

#programista15k #programista25k #programista30k #programista50k #programista0k

Wszystko

Najnowsze

Archiwum

3

Ciekawa, interaktywna strona do nauki Veriloga (tak, wiem - to #programowanie jest mocno naciągane)

z3

Pierwszy odcinek kursu SystemVerilog. Dowiemy się co to za język i do czego jest używany. Napiszemy także nasz pierwszy projekt i przeprowadzimy jego symulację w programie ModelSim.

z

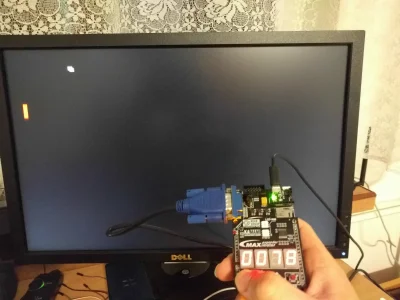

źródło: comment_gmmOFk8ZqOb2VAS6aZLHlwiwl4Bv5QKk.jpg

Pobierz

if(rst || cnt[18])Regulamin

Reklama

Kontakt

O nas

FAQ

Osiągnięcia

Ranking

#fpga #verilog #vhdl #elektronika

@yungdupa:

Jak mawia stare chińskie przysłowie:

"Droga na szczyt wiedzie pod górę."