Wszystko

Najnowsze

Archiwum

@wonsz_smieszek: skoro piszesz, ze jedno i drugie dało radę to jak ci wygodniej.

- 1

@wonsz_smieszek: nie ma za bardzo wyboru i musisz nauczyć się przynajmniej podstaw jednego i ogarniać w drugim, IMO.

W projekcie bardzo prawdopodobne że będzie mieszany VHDL i Verilog choćby z uwagi na to, że niektóre moduły Altery generują tylko np. Veriloga.

Ogółem to wyczytałem, że Verilog jest językiem w którym można zrealizować więcej niskopoziomowych rzeczy (zbliżone w kierunku poziomu już tranzystorowego), a VHDL jest językiem z mocno rozwiniętą abstrakcyjnością, przez

W projekcie bardzo prawdopodobne że będzie mieszany VHDL i Verilog choćby z uwagi na to, że niektóre moduły Altery generują tylko np. Veriloga.

Ogółem to wyczytałem, że Verilog jest językiem w którym można zrealizować więcej niskopoziomowych rzeczy (zbliżone w kierunku poziomu już tranzystorowego), a VHDL jest językiem z mocno rozwiniętą abstrakcyjnością, przez

- 1

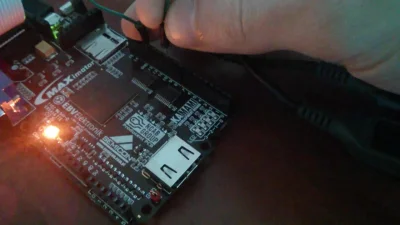

Jeżeli ktoś się nia załapał na cebulę z Maximatorem, to polecam się #fpga ( ͡° ͜ʖ ͡°)

http://allegro.pl/maximator-fpga-max10-expander-kamami-usb-blaster-i6575433870.html

http://allegro.pl/maximator-fpga-max10-expander-kamami-usb-blaster-i6575433870.html

- 2

Mirki potrzebuję Waszej pomocy, sytuacja jest następująca:

Mam do zrobienia system z przetwarzania obrazu. Obraz ma być czytany z kamery 1024x256 pikseli, w odcieniach szarości. Będzie trzeba na nim rozpoznawać jasne kółko na ciemnym tle oraz ciemne punkty w tym jasnym kółku. Kółko powinno mieć zwykle średnicę około 200 px. Może się zdarzać, że będzie tylko częściowo widoczne kółko i właśnie cała zabawa na tym polega, żeby wiedzieć gdzie jest środek tego kółka

Mam do zrobienia system z przetwarzania obrazu. Obraz ma być czytany z kamery 1024x256 pikseli, w odcieniach szarości. Będzie trzeba na nim rozpoznawać jasne kółko na ciemnym tle oraz ciemne punkty w tym jasnym kółku. Kółko powinno mieć zwykle średnicę około 200 px. Może się zdarzać, że będzie tylko częściowo widoczne kółko i właśnie cała zabawa na tym polega, żeby wiedzieć gdzie jest środek tego kółka

@navry: technologia to w tym przypadku najmniejszy problem. Ja bym raczej skupił się na algorytmie i ewentualnie samym schemacie działania aplikacji a dopiero później martwił o technologię. Pytanie podstawowe dlaczego chcesz to robić na fpga? To ma pracować w czasie rzeczywistym? Może lepiej byłoby pobawić się z logiką rozmytą? Algorytmy rozpoznawania krawędzi i te sprawy...

- 0

@navry: problem wygląda dość prosto a jeżeli analiza ma się wyrabiać w sekundę to w ogóle bajka :) zrobisz to bez trudu na jakimś raspberrypi, słabym smartfonie a na stacjonarnym/przemysłowym PC będzie działać 3 rzędy wielkości za szybko ;-)

Tak jak pisze @adam-bojarski, najpierw zrób i przetestuj algorytm a potem go zaimplementuj docelowo. Więc tak:

1) zbierz dane, bez tego nie ruszysz, najlepiej jeżeli będą to dane (obrazki) z rzeczywistego

Tak jak pisze @adam-bojarski, najpierw zrób i przetestuj algorytm a potem go zaimplementuj docelowo. Więc tak:

1) zbierz dane, bez tego nie ruszysz, najlepiej jeżeli będą to dane (obrazki) z rzeczywistego

Mirki z #elektronika #fpga #programowanie

Chcę się zabrać za fpga i stoję przed wyborem zestawu uruchomieniowego. Zastanawiam się między dwoma

https://kamami.pl/zestawy-uruchomieniowe/103164-basys2-100.html

https://kamami.pl/zestawy-uruchomieniowe/103137-basys2-250.html

Czy te 150 tysięcy bramek robi dużą różnicę i warto dołożyć 230zł? A może jest jakiś lepszy zestaw w podobnej cenie?

Chcę się zabrać za fpga i stoję przed wyborem zestawu uruchomieniowego. Zastanawiam się między dwoma

https://kamami.pl/zestawy-uruchomieniowe/103164-basys2-100.html

https://kamami.pl/zestawy-uruchomieniowe/103137-basys2-250.html

Czy te 150 tysięcy bramek robi dużą różnicę i warto dołożyć 230zł? A może jest jakiś lepszy zestaw w podobnej cenie?

- 0

@ajron_men: To wychodzi na to, że ten drugi układ ma tylko ok. 5000 LUTów... Za ARM się na razie nie chcę zabierać, z AVR sobie ledwo co radzę i nawet takich zestawów ARM+FPGA nie widziałem.

Edit:

Jednak znalazłem:

https://kamami.pl/zestawy-uruchomieniowe/558403-terasic-de0-nano-soc-kit-zestaw-startowy-z-ukladem-fpga-z-rodziny-altera-cyclone-v-soc.html

ale nie mam pojęcia co o tym sądzić.

Edit:

Jednak znalazłem:

https://kamami.pl/zestawy-uruchomieniowe/558403-terasic-de0-nano-soc-kit-zestaw-startowy-z-ukladem-fpga-z-rodziny-altera-cyclone-v-soc.html

ale nie mam pojęcia co o tym sądzić.

Wydaje mi się, że dużo lepsza inwestycja. Zwłaszcza, że pozwala opanować zarówno ARM jak i projektowanie zrównoleglonych algorytmów na FPGA. Zastosowanie takiego SOC daje dużo więcej możliwości - np. stawiasz system na up, a rzeczy, które potrzebują dużo mocy obliczeniowej wykonujesz na układzie programowalnym (szyfrowanie, filtracja etc.). Ale wiadomo, że taką zabawę rozpoczyna się od zapalenia diody z poziomu jakiegoś peta-linuxa. :)

#ciekawostki #ovh #fpga #serwery #apache #webdev

Apache akcelerowany na FPGA?

OVH już sprzedaje takie maszyny

https://www.runabove.com/FPGAaaS.xml

Apache akcelerowany na FPGA?

OVH już sprzedaje takie maszyny

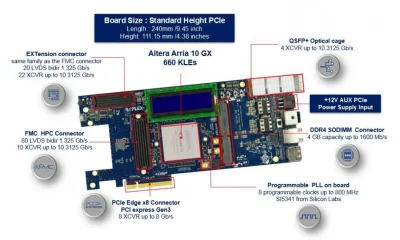

ALTERA Arria 10 GX 1150 FPGA integrates 1150k Logic Elements (LE) and 2x4GB of memory.

https://www.runabove.com/FPGAaaS.xml

źródło: comment_7kTORtWHh95GUFvK1kDTPkQO12Q22YS9.jpg

PobierzSą jakieś godne polecenia firmy w #poznan związane z systemami wbudowanymi, FPGA (inżynierka z Xilinxem), IoT i tego typu rzeczami? Na razie znalazłem AntMirko ( ͡º ͜ʖ͡º) Jest coś jeszcze? Chodzi głównie o staże/praktyki i ew. punkt zaczepienia do dalszej pracy. Średnio widzę siebie jako webdev i twórca systemów zarządzania bazami danych do zarządzania modułami zarządzania albo innych wiedźminów, jakoś bardziej wolę jumpy w asemblerze

- 21

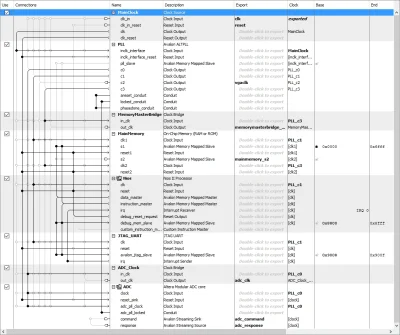

Projekt oscyloskopu cyfrowego. Trochę czasu minęło odkąd wszystko zacząłem, jakiś miesiąc - przez ten czas do ogarnięcia było sporo dużych i drobnych problemów, które potrafiły zająć cały dzień.. Zdecydowanie projektowanie czegoś na FPGA wymaga dużej trzeźwości umysłu. W sumie spędziłem może nad tym projektem z 100 roboczogodzin.

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

źródło: comment_yKlgVPc8UOU7D9ZREo85MjJeETRcFpTB.jpg

PobierzKurde, bo ja zaraz oszaleje. Vivado jest w końcu darmowy, czy nie? Czy to działa jakoś na zasadzie Visual Studio, że podstawowa funkcjonalność jest darmowa, a jakieś bajery za dodatkową opłatą? Bo chcę zamówić płytkę Basys3, a jest jakaś wersja droższa z pakietem Vivado. A wykładowca mówił, że Vivado jest darmowe. Wystarczy ten darmowy Vivado do konfigurowania tego Basysa3 z Artixem?

#fpga #elektronika #xilinx

#fpga #elektronika #xilinx

5

Amiga 500: Vampire 500 V2 - trwają testy (wideo)

Trwają testy karty turbo FPGA Vampire dla Amigi 500, o której wspominaliśmy w lutym tego roku. W naszej galerii znajdziecie zdjęcia wyprodukowanej już karty oraz wyniki z SysInfo.

z- 0

- #

- #

- #

- #

- #

- #

- 27

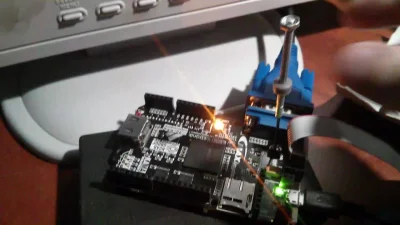

Elo Mirko. Pamiętacie jak tydzień temu mówiłem, że idę w kierunku oscyloskopu? Nie kłamałem i swoje przez ten tydzień zrobiłem ( ͡° ͜ʖ ͡°) Jest i gfycat na dole ( ͡° ͜ʖ ͡°) Pod punktami informacje co dalej z projektem

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

źródło: comment_YX1P0z92fKFIu29AN2sOiZcdHCEHN66T.jpg

Pobierz- 1

@Visher: Nie chcę Ci podcinać skrzydeł ale raczej nie masz szans konkurować na rynku oscyloskopów USB z chińczykami (chociażby). Za $100 można już na aliexpress przebierać w modelach, a według Twoich wyliczeń (zakładam, że są poprawne) nie pokrywa to nawet kosztów komponentów. A gdzie produkcja (produkt z układami BGA trudno będzie sprzedać jako kit), testowanie, pisanie softu czy zysk. Nie mówiąc o inwestorze/dystrybutorze, który będzie też chciał swoją działkę. Polecam

- 1

@olewales: odnosząc się do rynku konsumentów i przedsiębiorców bardziej miałem na myśli to, czy budowa czegoś takiego gdziekolwiek by się przydała. Głównie informacja, czy ktoś by chciał mieć wygodny interfejs w komputerze, bo choć tak naprawdę byłem tylko w jednym warsztacie elektronicznym pewnej firmy z różnymi "poważnymi" maszynami: stanowisko na sito do pasy lutowniczej, piec do lutowania (w formie taśmy), maszyna do automatycznego nakładania elementów SMD i parę innych podobnych,

- 14

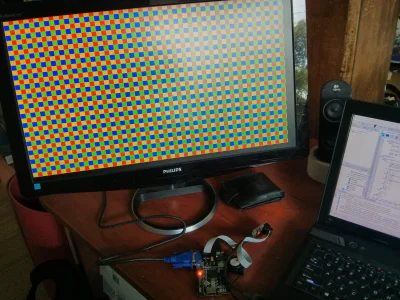

UART skończony, teraz pora na 8-kolorowe VGA :-)

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

źródło: comment_ljITNk4VBphsl5BDIF9Wvfzf2G1Q8j4v.jpg

Pobierz- 2

Hej #fpga, chciałbym kupić jakąś dobrą płytkę projektową. Polećcie mi sklep w Polsce/Europie. Polecenie modelu też chętnie przyjmę.

- 1

@matador: kamami.pl, bardzo tania altera - https://kamami.pl/zestawy-uruchomieniowe/561438-zestaw-maximator-maximator-expander-kamami-usb-blaster.html?search_query=maximator&results=18 (nie wiem kiedy zrestockują),

dobry xilinx (trzeba studenta jakiegoś bo 2x taniej) - https://kamami.pl/zestawy-uruchomieniowe/234121-zestaw-basys3-z-fpga-artix-7-edu.html?search_query=basys3&results=4

dobry xilinx (trzeba studenta jakiegoś bo 2x taniej) - https://kamami.pl/zestawy-uruchomieniowe/234121-zestaw-basys3-z-fpga-artix-7-edu.html?search_query=basys3&results=4

A ja od siebie polecę kurs dotyczący tej płytki http://roboblog.eu/2016/01/16/fpga/

PS. Płytka już niedługo powinna się pojawić na magazynie ( ͡° ͜ʖ ͡°)

PS. Płytka już niedługo powinna się pojawić na magazynie ( ͡° ͜ʖ ͡°)

- 7

UART, ciągle UART. Przyczynę poprzedniego problemu znalazłem, zawiniło txIdle które było w stanie wysokim przez dwa cykle i dwukrotnie zwiększyło indeks po pierwszym znaku, przeskakując na trzeci. Wynikało to ze złego przekazywania zmiennej w procesie do sygnału - wołam @olewales

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

źródło: comment_Uttil5ouGIUCZP1dJIAxofc3OqMllhy7.jpg

Pobierz- 1

@olewales: no i znalazłem problem...

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

- 1

Siemka Mirki i Mirabelki.

Własnie skończyłem tłumaczenie swojego pierwszego artykułu http://roboblog.eu/en/2016/05/15/fpga-tutorial-0/

Co o tym sądzicie? Jest w miarę znośnie? Proszę dajcie znać jeżeli możecie.

#tlumaczenie #angielski #elektronika

Własnie skończyłem tłumaczenie swojego pierwszego artykułu http://roboblog.eu/en/2016/05/15/fpga-tutorial-0/

Co o tym sądzicie? Jest w miarę znośnie? Proszę dajcie znać jeżeli możecie.

#tlumaczenie #angielski #elektronika

@Maciek-roboblog: Very good! I like It!(sry for my english)

- 1

@Maciek-roboblog: Przeczytałem tylko część do pierwszego screena i sporo błędów i dużo zdań brzmiących mocno nienaturalnie + article.

Od literówek (to akurat gdzieś dalej w tekście, przypadkiem rzuciło się w oczy

po różne "takie

Od literówek (to akurat gdzieś dalej w tekście, przypadkiem rzuciło się w oczy

you will lern

po różne "takie

- 8

Zmagania z FPGA i VHDL ciąg dalszy ;-)

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

źródło: comment_WDOwVE0BJ7UQVWtuR68VNtf4y3YOvDg6.jpg

PobierzHej mirki, istnieje jakiś sposób na implementację wyjść LVDS na pinach 0-16 maximatora? Konwertery 3.3/5v chyba to uniemożliwiają?

#fpga #maximator #elektronika

#fpga #maximator #elektronika

- 1

- 0

Rezystory w sensie dzielnik napięcia aby uzyskać 0v i ~150mv?

- 13

No, to pierwszy krok w FPGA mam już za sobą - nie mniej jednak jeszcze mnóstwo przede mną. Na ten moment udało mi się zrobić całkiem zgrabny debouncer przycisku z podziałem na sam debouncer i licznik, który to zaaplikowałem dla czterech pinów. Kod jest tu:

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

źródło: comment_KloDqPjcmjE27kpVgI9EuTbCQS4ovtXF.jpg

Pobierz- 1

- 0

@fhrh: ciężko mi odpowiedzieć, na Politechnice mam dostęp do biblioteki i tam wygrzebuję informacje z paru książek naraz i łącze to w całość. Żadna nie nauczyła mnie sama z siebie tego co tu pokazałem - też nie czytałem żadnej od początku do końca. Do tego internet - videotutoriale na YT, stackoverflow-podobne serwisy, gotowe programy...

- 2

Piszę sobie licznik do debouncera przycisku (napisałem sam debouncer w jednym pliku i działał, ale teraz chcę podzielić to na dwa pliki i dwie osobne jednostki: uogólniony licznik i debouncer) i mam problem z instrukcją:

Kod wygląda tak:

http://pastebin.com/UzSgSGPi

Q <= '1' when (clkCounter = target) else '0';Kod wygląda tak:

http://pastebin.com/UzSgSGPi

- 9

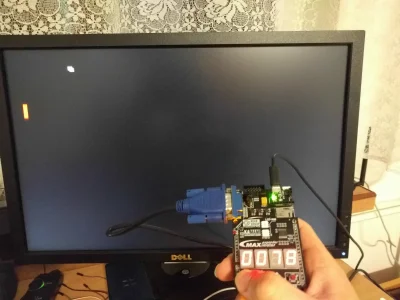

Fajne to FPGA.

Na zdjęciu Pong jednoosobowy, w którym zasady są zmyślone i punkty nie mają znaczenia :)

#fpga #verilog

i #nieprogramowanie bo to #synteza ;)

Na zdjęciu Pong jednoosobowy, w którym zasady są zmyślone i punkty nie mają znaczenia :)

#fpga #verilog

i #nieprogramowanie bo to #synteza ;)

źródło: comment_gmmOFk8ZqOb2VAS6aZLHlwiwl4Bv5QKk.jpg

Pobierz- 3

@a231: czekałem na kolejne części kursu, ale się nie doczekałem i wziąłem sprawy w swoje ręce. Kurs Veriloga + konfiguracja JTAGa, nauka jak działa mapowanie pinów, ip i tego typu zagadnienia i jazda.

Polecam filmik od Ben Hecka.

Polecam filmik od Ben Hecka.

Zapraszam Was do najnowszego artykułu dotyczącego #fpga ( ͡° ͜ʖ ͡°)

http://roboblog.eu/2016/10/09/fpga-poradnik-4/