Elo Mirko. Pamiętacie jak tydzień temu mówiłem, że idę w kierunku oscyloskopu? Nie kłamałem i swoje przez ten tydzień zrobiłem ( ͡° ͜ʖ ͡°) Jest i gfycat na dole ( ͡° ͜ʖ ͡°) Pod punktami informacje co dalej z projektem

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

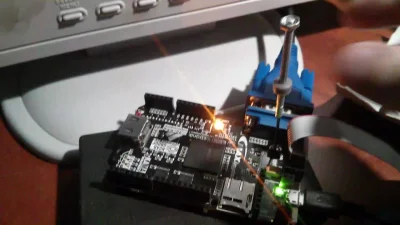

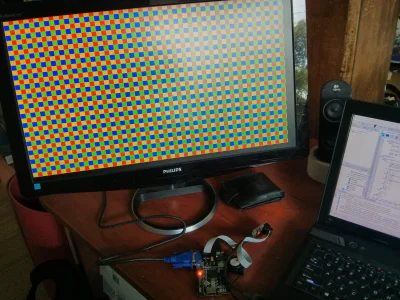

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

źródło: comment_yKlgVPc8UOU7D9ZREo85MjJeETRcFpTB.jpg

Pobierz@Visher: