#elektronika #debilizm #zmeczenie #fpga #tyleprzegrac

To óczócie gdy układ działa już od dłuższego czasu i jakieś kilkanaście ostatnich prób badasz czemu ten chory s------l wygląda jakby się zdesynchronizował przy komunikacji, a przy zrobieniu echa działa wszystko jak trzeba. A to terminal wysyłał w ASCII a nie w binarce (╯︵╰,)

Usilnie wbijałem ciąg binarny typu "00001000" z oczekiwaniem, że

To óczócie gdy układ działa już od dłuższego czasu i jakieś kilkanaście ostatnich prób badasz czemu ten chory s------l wygląda jakby się zdesynchronizował przy komunikacji, a przy zrobieniu echa działa wszystko jak trzeba. A to terminal wysyłał w ASCII a nie w binarce (╯︵╰,)

Usilnie wbijałem ciąg binarny typu "00001000" z oczekiwaniem, że

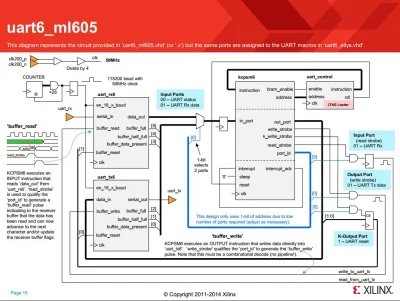

Wiadomo może czemu nadajnik UART wysyła mi taki szum na terminal jak tylko zaimplementuję go w układzie? Co może być źródłem czegoś takiego? On nie powinien w ogóle nadawać danych dopóki nie otrzyma ich przez RXD, bo ma robić echo. Tymczasem w momencie włączenia układu on już n--------a jakimś spamem, mimo, że TXD powinno być na stałej wartości 1 i nic nie robić.

źródło: comment_oCxsf8X7ljucIXHXkvnoH3JHqWe0gQ92.jpg

Pobierz