Wszystko

Najnowsze

Archiwum

@wonsz_smieszek: skoro piszesz, ze jedno i drugie dało radę to jak ci wygodniej.

- 1

@wonsz_smieszek: nie ma za bardzo wyboru i musisz nauczyć się przynajmniej podstaw jednego i ogarniać w drugim, IMO.

W projekcie bardzo prawdopodobne że będzie mieszany VHDL i Verilog choćby z uwagi na to, że niektóre moduły Altery generują tylko np. Veriloga.

Ogółem to wyczytałem, że Verilog jest językiem w którym można zrealizować więcej niskopoziomowych rzeczy (zbliżone w kierunku poziomu już tranzystorowego), a VHDL jest językiem z mocno rozwiniętą abstrakcyjnością, przez

W projekcie bardzo prawdopodobne że będzie mieszany VHDL i Verilog choćby z uwagi na to, że niektóre moduły Altery generują tylko np. Veriloga.

Ogółem to wyczytałem, że Verilog jest językiem w którym można zrealizować więcej niskopoziomowych rzeczy (zbliżone w kierunku poziomu już tranzystorowego), a VHDL jest językiem z mocno rozwiniętą abstrakcyjnością, przez

Zna ktoś jakiś dobry przewodnik po języku #vhdl? Może być po angielsku.

#pytanie #kiciochpyta #elektronika #elektrotechnika

#pytanie #kiciochpyta #elektronika #elektrotechnika

- 0

- 21

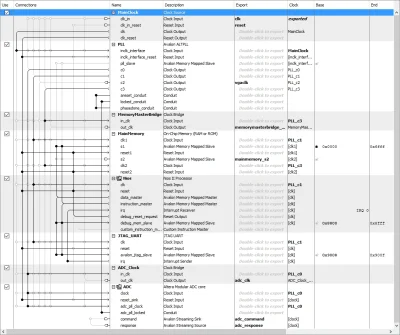

Projekt oscyloskopu cyfrowego. Trochę czasu minęło odkąd wszystko zacząłem, jakiś miesiąc - przez ten czas do ogarnięcia było sporo dużych i drobnych problemów, które potrafiły zająć cały dzień.. Zdecydowanie projektowanie czegoś na FPGA wymaga dużej trzeźwości umysłu. W sumie spędziłem może nad tym projektem z 100 roboczogodzin.

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

źródło: comment_yKlgVPc8UOU7D9ZREo85MjJeETRcFpTB.jpg

Pobierz#elektronika #vhdl

Mam pytanie czy da się jakoś w vhdlu przypisać pewnym wartościom przypisać nazwy pewnym wartościom? Czyli zamienić ="000100" na =reset . Czy coś takiego w ogóle istnieje?

Mam pytanie czy da się jakoś w vhdlu przypisać pewnym wartościom przypisać nazwy pewnym wartościom? Czyli zamienić ="000100" na =reset . Czy coś takiego w ogóle istnieje?

- 27

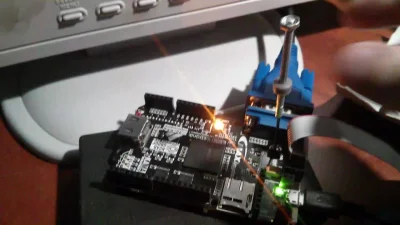

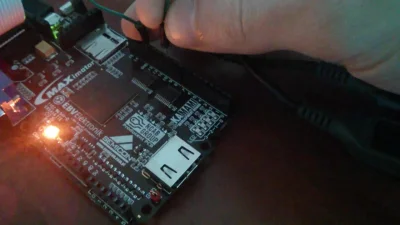

Elo Mirko. Pamiętacie jak tydzień temu mówiłem, że idę w kierunku oscyloskopu? Nie kłamałem i swoje przez ten tydzień zrobiłem ( ͡° ͜ʖ ͡°) Jest i gfycat na dole ( ͡° ͜ʖ ͡°) Pod punktami informacje co dalej z projektem

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

źródło: comment_YX1P0z92fKFIu29AN2sOiZcdHCEHN66T.jpg

Pobierz- 1

@Visher: Nie chcę Ci podcinać skrzydeł ale raczej nie masz szans konkurować na rynku oscyloskopów USB z chińczykami (chociażby). Za $100 można już na aliexpress przebierać w modelach, a według Twoich wyliczeń (zakładam, że są poprawne) nie pokrywa to nawet kosztów komponentów. A gdzie produkcja (produkt z układami BGA trudno będzie sprzedać jako kit), testowanie, pisanie softu czy zysk. Nie mówiąc o inwestorze/dystrybutorze, który będzie też chciał swoją działkę. Polecam

- 1

@olewales: odnosząc się do rynku konsumentów i przedsiębiorców bardziej miałem na myśli to, czy budowa czegoś takiego gdziekolwiek by się przydała. Głównie informacja, czy ktoś by chciał mieć wygodny interfejs w komputerze, bo choć tak naprawdę byłem tylko w jednym warsztacie elektronicznym pewnej firmy z różnymi "poważnymi" maszynami: stanowisko na sito do pasy lutowniczej, piec do lutowania (w formie taśmy), maszyna do automatycznego nakładania elementów SMD i parę innych podobnych,

- 14

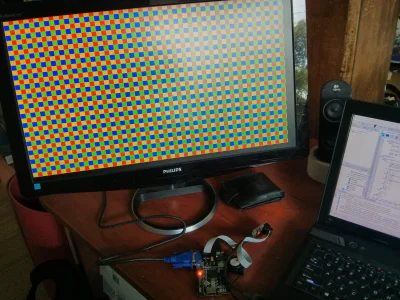

UART skończony, teraz pora na 8-kolorowe VGA :-)

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

źródło: comment_ljITNk4VBphsl5BDIF9Wvfzf2G1Q8j4v.jpg

Pobierz- 7

UART, ciągle UART. Przyczynę poprzedniego problemu znalazłem, zawiniło txIdle które było w stanie wysokim przez dwa cykle i dwukrotnie zwiększyło indeks po pierwszym znaku, przeskakując na trzeci. Wynikało to ze złego przekazywania zmiennej w procesie do sygnału - wołam @olewales

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

źródło: comment_Uttil5ouGIUCZP1dJIAxofc3OqMllhy7.jpg

Pobierz- 1

@olewales: no i znalazłem problem...

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

- 1

- 8

Zmagania z FPGA i VHDL ciąg dalszy ;-)

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

źródło: comment_WDOwVE0BJ7UQVWtuR68VNtf4y3YOvDg6.jpg

Pobierz- 13

No, to pierwszy krok w FPGA mam już za sobą - nie mniej jednak jeszcze mnóstwo przede mną. Na ten moment udało mi się zrobić całkiem zgrabny debouncer przycisku z podziałem na sam debouncer i licznik, który to zaaplikowałem dla czterech pinów. Kod jest tu:

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

źródło: comment_KloDqPjcmjE27kpVgI9EuTbCQS4ovtXF.jpg

Pobierz- 1

- 0

@fhrh: ciężko mi odpowiedzieć, na Politechnice mam dostęp do biblioteki i tam wygrzebuję informacje z paru książek naraz i łącze to w całość. Żadna nie nauczyła mnie sama z siebie tego co tu pokazałem - też nie czytałem żadnej od początku do końca. Do tego internet - videotutoriale na YT, stackoverflow-podobne serwisy, gotowe programy...

- 2

Piszę sobie licznik do debouncera przycisku (napisałem sam debouncer w jednym pliku i działał, ale teraz chcę podzielić to na dwa pliki i dwie osobne jednostki: uogólniony licznik i debouncer) i mam problem z instrukcją:

Kod wygląda tak:

http://pastebin.com/UzSgSGPi

Q <= '1' when (clkCounter = target) else '0';Kod wygląda tak:

http://pastebin.com/UzSgSGPi

Coś takiego jest niedozwolone w Verilogu?

Bo tutaj jest coś podobnego, tyle, że w else, a mi nie działa w ifie.

http://www.asic-world.com/verilog/vbehave2.html

#fpga #verilog #vhdl #hdl

if(rst || cnt[18])Bo tutaj jest coś podobnego, tyle, że w else, a mi nie działa w ifie.

http://www.asic-world.com/verilog/vbehave2.html

#fpga #verilog #vhdl #hdl

- 0

@JayCube: chyba znalazłem. Pierwszy if w bloku always powinien dotyczyć tylko reseta.

@ortofosforan: dlatego mówię że zależy gdzie. Jak dasz always @(cnt or rst) może przejdzie. Ale jak kompilator mówi nie, to nie...

- 1

Chę zacząć swoją przygodę z VHDLem i poprowadzić ją w kierunku DSP.

Macie jakieś dobre kursy, tutoriale, ćwiczenia? Jakie środowisko wybrać? Jest sens działaś na samym symulatorze, czy szukać sprzętu? (jakiego?)

#kiciochpyta #programowanie #elektronika #vhdl #uczsiezwykopem

Macie jakieś dobre kursy, tutoriale, ćwiczenia? Jakie środowisko wybrać? Jest sens działaś na samym symulatorze, czy szukać sprzętu? (jakiego?)

#kiciochpyta #programowanie #elektronika #vhdl #uczsiezwykopem

@Leniek: nie wiem czy dobre, bo nigdy nie znalazłem chęci ani potrzeby zabrać się za do i leży w zakładkach:

http://users.ece.gatech.edu/sudha/book/starters-guide/

http://www.seas.upenn.edu/~ese171/vhdl/vhdl_primer.html

http://www.myhdl.org/

http://users.ece.gatech.edu/sudha/book/starters-guide/

http://www.seas.upenn.edu/~ese171/vhdl/vhdl_primer.html

http://www.myhdl.org/

@Leniek: nie robie tego zawodowo, trochę dłubię w audio na płytce de1 od terasica, jestem z niej zadowolony. Myślę że dobrym projektem na start są filtry. Pisałem w verilogu

- 4

Mirki dostałem zadanie z programowania FPGA, uwaga.

"Jaką czynność wykonuje Pani na poniższym rysunku - uzasadnić"

Rozchodzi się o Panią z tego linku link

Prowadzący

"Jaką czynność wykonuje Pani na poniższym rysunku - uzasadnić"

Rozchodzi się o Panią z tego linku link

Prowadzący

@lupoo: ucieka z kuchni

Ogłoszenie z mojej siecii na linkedin #vhdl #innyswiat ;)

#pracazagranica #emigracja #heheszki

Any Hardware Engineer looking for an 18 month contract in Dublin, let me know. VHDL, FPGAs, schematic design, etc. All the good stuff!

#pracazagranica #emigracja #heheszki

- 1

#elektronika #vhdl

Wie ktoś może, dlaczego w tym układzie nie chce mi wrócić do standby po wykonaniu zadania, tylko trzyma cały czas frame na wyjściu?

https://gist.github.com/anonymous/867c62fb4db6909560f2

Taki

Wie ktoś może, dlaczego w tym układzie nie chce mi wrócić do standby po wykonaniu zadania, tylko trzyma cały czas frame na wyjściu?

https://gist.github.com/anonymous/867c62fb4db6909560f2

Taki

źródło: comment_z1pTstbwTMurpl70Kc71Z72MI8S4nNiK.jpg

Pobierz- 0

W tej skali lepiej to widać. Jak widać po liniach sygnałowych wyprowadzone dane są poprawne, ale nie zeruje wyjścia...

źródło: comment_GJnVcrj1RTEstrf4fZ80eV76LR2blPpU.jpg

Pobierz- 0

No curwa w końcu ;_;

Mocno uważajcie na sensitivity list w procesach. Brakowało po prostu w ostatnim procesie sensitivity od FRAME, przez co nie aktualizował stanu. Natomiast, żeby potem nie aktualizował z każdym tickiem (bo jak procek albo coś innego przypadkowo sprawdzi to dostanie bzdury), trzeba było dodać jeszcze jedną kontrolkę przy zmianie stanu.

Mocno uważajcie na sensitivity list w procesach. Brakowało po prostu w ostatnim procesie sensitivity od FRAME, przez co nie aktualizował stanu. Natomiast, żeby potem nie aktualizował z każdym tickiem (bo jak procek albo coś innego przypadkowo sprawdzi to dostanie bzdury), trzeba było dodać jeszcze jedną kontrolkę przy zmianie stanu.

źródło: comment_05omvx8znGmCI1UKRcNH3h8fU2fGujKU.jpg

Pobierz- 3

#elektronika #vhdl

Pytanie kolejne z dziedziny RSa.

http://www.bealto.com/fpga-uart_rx.html

Wzoruję się na tym UARTcie robiąc własny. Generalnie ma on taktowanie 16x większe niż jest BAUD na komunikacji. No spoko. I teraz działanie ma takie, że sprawdza co 8 ticków stan bitu na RXD jak dostanie wcześniej bit startu. No spoko. No tylko problem jest w tym, że ten bit wypada po 8 tickach aby znajdował się możliwie na środku

Pytanie kolejne z dziedziny RSa.

http://www.bealto.com/fpga-uart_rx.html

Wzoruję się na tym UARTcie robiąc własny. Generalnie ma on taktowanie 16x większe niż jest BAUD na komunikacji. No spoko. I teraz działanie ma takie, że sprawdza co 8 ticków stan bitu na RXD jak dostanie wcześniej bit startu. No spoko. No tylko problem jest w tym, że ten bit wypada po 8 tickach aby znajdował się możliwie na środku

- 2

#elektronika #vhdl

Próbuję właśnie "zaprojektować" bufor do RS232. Początkowo myślałem, żeby zrobić to na rejestrze przesuwnym, ale przypomniałem sobie, że przecież w VHDLu istnieje pętla for. Tylko teraz zastanawiam się jak on to dokładnie będzie robił.

Generalnie na ten moment jak pojawi się bit startu na linii RXD, to w następnym takcie zegara nastąpi przejście w stan odebrania. Teraz musimy z każdym tyknięciem ładować do ramki poszczególne bity, a gdy

Próbuję właśnie "zaprojektować" bufor do RS232. Początkowo myślałem, żeby zrobić to na rejestrze przesuwnym, ale przypomniałem sobie, że przecież w VHDLu istnieje pętla for. Tylko teraz zastanawiam się jak on to dokładnie będzie robił.

Generalnie na ten moment jak pojawi się bit startu na linii RXD, to w następnym takcie zegara nastąpi przejście w stan odebrania. Teraz musimy z każdym tyknięciem ładować do ramki poszczególne bity, a gdy

- 1

- 0

@Khaine: nie chce Cie denerwowac, ale w prawilnych mirkokontrolerach kazdy bit jest probkowany 3 razy, w rownych odstepach czasu, zeby uniknac bledow. decyzja o poziomie logicznym bitu zapada na zasadzie wiekszosci 'glosow' czastkowych.

- 2

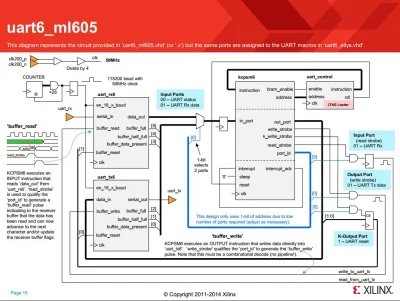

#elektronika #fpga #vhdl

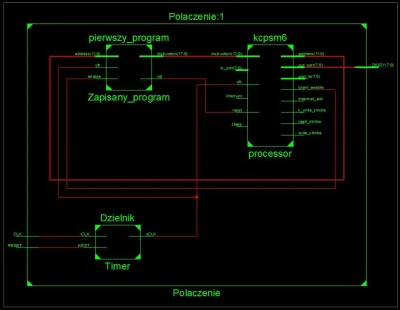

Tak wygląda schemat gotowego UARTa do procka przy którym obecnie dłubię (bo on sam swojego bufora nie ma). I generalnie jedna rzecz mnie patrząc na to zastanawia. Z tego co widzę odczyt wejścia następuje na życzenie procka. Nie lepiej jest mu dać przerwanie jak bufor się zapełni? No bo w ten sposób to on musi cały czas żądać odczytu (gdzieś co 160 taktów

Tak wygląda schemat gotowego UARTa do procka przy którym obecnie dłubię (bo on sam swojego bufora nie ma). I generalnie jedna rzecz mnie patrząc na to zastanawia. Z tego co widzę odczyt wejścia następuje na życzenie procka. Nie lepiej jest mu dać przerwanie jak bufor się zapełni? No bo w ten sposób to on musi cały czas żądać odczytu (gdzieś co 160 taktów

źródło: comment_MIvfjHWF4l2ciAGcS5WpE61xNkzd4TI3.jpg

Pobierz- 1

#elektronika #fpga #vhdl

Chcę sobie otworzyć komunikację (na razie ultra prostą, po prostu aby zobaczyć czy bangla) z prockiem PicoBlaze zaimplementowanym w FPGA po RS232.

RSa mam na przejściówce USB->RS232, ale to nie ma raczej większego znaczenia. Do komunikacji ze strony kompa chcę użyć terminala Hercules, ale to też nie ma większego znaczenia raczej. Jako, że mam taktowanie 27 MHz na kwarcu, to zrobiłem sobie timer, który dzieli

Chcę sobie otworzyć komunikację (na razie ultra prostą, po prostu aby zobaczyć czy bangla) z prockiem PicoBlaze zaimplementowanym w FPGA po RS232.

RSa mam na przejściówce USB->RS232, ale to nie ma raczej większego znaczenia. Do komunikacji ze strony kompa chcę użyć terminala Hercules, ale to też nie ma większego znaczenia raczej. Jako, że mam taktowanie 27 MHz na kwarcu, to zrobiłem sobie timer, który dzieli

źródło: comment_l4M26OXImR0wH70eAO4GDziBrxQe8h6V.jpg

Pobierz- 1

@Khaine: i właśnie z tego powodu wybrałem pracę przy "miRkokontrolerach właściwych" zamiast bawić się w VHDL :)

- 0

Teraz jeszcze jest pytanie -> czy jak jest tam ten przetwornik RS232, to on mi usuwa bity startu i stopu, czy wywala z siebie 10 bitowe ramki? Bo teraz w sumie nie wiem też jak to potraktować. Czy ten układ komunikacyjny musi mi tylko sekwencyjnie przetwarzać sygnał seryjny na wektor, czy jeszcze bity stopu i startu wywalać?

@navry: taa, szczególnie pozbycie się błędów z kodu co ma 25 lat jest powszechne ;)