Aktywne Wpisy

konserwix +303

WielkiNos +361

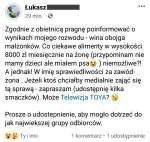

Ale się chłop wkopał dajcie spokój. Niektórzy to nie mają szczęścia.

#pieklomezczyzn #dyskryminacjamezczyzn #prawo #rozwod #zwiazki #alimenty

#pieklomezczyzn #dyskryminacjamezczyzn #prawo #rozwod #zwiazki #alimenty

źródło: temp_file8546865865444551401

Pobierz

Kawałek mojego kodu lata na tym chipie :)

#technologia #ciekawostki #programowanie #programista15k #pracait

@groman43: Naszego kodu.

@JayCube jeszcze kilka lat temu MediaTek robił bardzo często chip testowe. Ale udało się wszystko ustabilizować i zwykle chip działa od kopa prosto z fabryki (wiem, niewiarygodne xD).

Tak design został zaakceptowany przez TSMC. Mass volume production rozpoczyna się dopiero w przyszłym roku. To jest związane z kombinacją

@groman43: Zwaliłeś gruche do zbiornika z kodem? #pdk

@groman43: No to nie rozumiem, czyli jednak ten kod jeszcze nie lata bo nie ma chipu, czy macie jakieś testowe ingenering samples (MPW lub MLM)?

Poza tym, jeśli kod trzeba dostosować do zmian w chipie (nie zawsze to jest wymagane, czasem wystraczy zmienić kilka define), to testujemu wszystko na FPGA.

Znam ja te kilka define.. Później masz cala regresje na czerwono i szukaj co jest nie tak :)