Treść przeznaczona dla osób powyżej 18 roku życia...

Wszystko

Najnowsze

Archiwum

Banri

- 19

Meister431

- 1

Treść przeznaczona dla osób powyżej 18 roku życia...

Treść przeznaczona dla osób powyżej 18 roku życia...

- 21

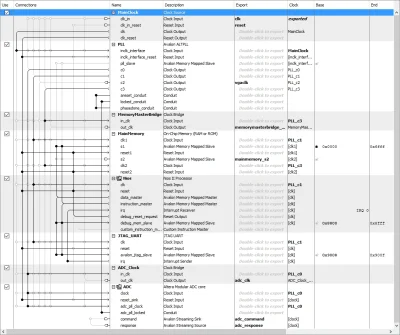

Projekt oscyloskopu cyfrowego. Trochę czasu minęło odkąd wszystko zacząłem, jakiś miesiąc - przez ten czas do ogarnięcia było sporo dużych i drobnych problemów, które potrafiły zająć cały dzień.. Zdecydowanie projektowanie czegoś na FPGA wymaga dużej trzeźwości umysłu. W sumie spędziłem może nad tym projektem z 100 roboczogodzin.

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

W ostatnim wpisie pokazałem Wam połączony moduł ADC, pamięć RAM i interfejs VGA, wraz z niewielką ilością systemu napisanego w VHDL. Dało to w efekcie prosty

źródło: comment_yKlgVPc8UOU7D9ZREo85MjJeETRcFpTB.jpg

Pobierz- 27

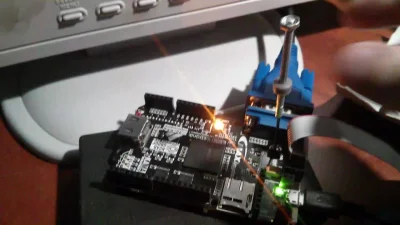

Elo Mirko. Pamiętacie jak tydzień temu mówiłem, że idę w kierunku oscyloskopu? Nie kłamałem i swoje przez ten tydzień zrobiłem ( ͡° ͜ʖ ͡°) Jest i gfycat na dole ( ͡° ͜ʖ ͡°) Pod punktami informacje co dalej z projektem

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

Trochę to trwało, bo wyszedł dodatek do Wiedźmina, ale pomimo tego udało mi się zrobić to co chciałem. Po kolei:

1) Nauczyłem się obsługiwać wbudowaną pamięć RAM w układach MAX10. Z dostępnych

źródło: comment_YX1P0z92fKFIu29AN2sOiZcdHCEHN66T.jpg

Pobierz- 1

@Visher: Nie chcę Ci podcinać skrzydeł ale raczej nie masz szans konkurować na rynku oscyloskopów USB z chińczykami (chociażby). Za $100 można już na aliexpress przebierać w modelach, a według Twoich wyliczeń (zakładam, że są poprawne) nie pokrywa to nawet kosztów komponentów. A gdzie produkcja (produkt z układami BGA trudno będzie sprzedać jako kit), testowanie, pisanie softu czy zysk. Nie mówiąc o inwestorze/dystrybutorze, który będzie też chciał swoją działkę. Polecam

- 1

@olewales: odnosząc się do rynku konsumentów i przedsiębiorców bardziej miałem na myśli to, czy budowa czegoś takiego gdziekolwiek by się przydała. Głównie informacja, czy ktoś by chciał mieć wygodny interfejs w komputerze, bo choć tak naprawdę byłem tylko w jednym warsztacie elektronicznym pewnej firmy z różnymi "poważnymi" maszynami: stanowisko na sito do pasy lutowniczej, piec do lutowania (w formie taśmy), maszyna do automatycznego nakładania elementów SMD i parę innych podobnych,

- 14

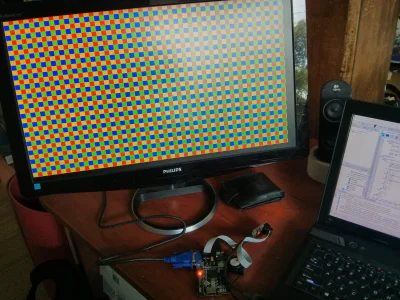

UART skończony, teraz pora na 8-kolorowe VGA :-)

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

I to nie byle jakie, bo od razu skok w 1920 x 1080 @ 60 fps - z zegarem 148,5 MHz! Bo mnie stać ;-)

Taki testowy ekran jak na obrazku zajmuje 50 na 8000 bloków logicznych w moim układzie FPGA. Choć brzmi to obiecująco jeżeli myśleć o tym ile można w taki układ wpakować funkcji, to mimo tego podobno szybko zaczyna miejsca brakować - zobaczymy.

źródło: comment_ljITNk4VBphsl5BDIF9Wvfzf2G1Q8j4v.jpg

Pobierz- 7

UART, ciągle UART. Przyczynę poprzedniego problemu znalazłem, zawiniło txIdle które było w stanie wysokim przez dwa cykle i dwukrotnie zwiększyło indeks po pierwszym znaku, przeskakując na trzeci. Wynikało to ze złego przekazywania zmiennej w procesie do sygnału - wołam @olewales

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

Problem rozwiązałem rozszerzając kod UART.vhd tak, aby przy dłuższym czasie trwania txIdle, nie przeskakiwało do kolejnego znaku. I fajnie, niby powinno działać.

Przy okazji nauczyłem się obsługiwać symulator ModelSim - jakie to

źródło: comment_Uttil5ouGIUCZP1dJIAxofc3OqMllhy7.jpg

Pobierz- 1

@olewales: no i znalazłem problem...

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

chodzi o to, że ponieważ txStart jest przez cały czas '1', to kopiuje sobie dane od razu po wysłaniu poprzednich. Natomiast UART.vhd dostarcza je jeden cykl później. Taka mała zmiana rozwiązała problem: http://pastebin.com/za5KZVAY

:)

- 1

- 8

Zmagania z FPGA i VHDL ciąg dalszy ;-)

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

Tym razem rzuciłem sobie wyzwanie napisać UARTa, poszło całkiem sprawnie i czuję większa swobodę w tym języku konfiguracji. Póki co zaimplementowałem samo nadawanie które na ogół działa, cechuje się jednak dziwnym błędem - zawsze wcina drugi znak. Jakikolwiek by nie był, cokolwiek by przed nim nie stało.. Pozostałe znaki w napisach o różnej długości są spoko, problem przy różnych baudach (testowałem 9600 i 38400).

źródło: comment_WDOwVE0BJ7UQVWtuR68VNtf4y3YOvDg6.jpg

Pobierz- 13

No, to pierwszy krok w FPGA mam już za sobą - nie mniej jednak jeszcze mnóstwo przede mną. Na ten moment udało mi się zrobić całkiem zgrabny debouncer przycisku z podziałem na sam debouncer i licznik, który to zaaplikowałem dla czterech pinów. Kod jest tu:

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

http://pastebin.com/fB0nYThM

Wszelkie uwagi mile widziane :) Staram się jeszcze zrozumieć sens podziału na jednostki, architektury i komponenty oraz jak nimi operować. Konkretnie sposób w jaki dochodzi do instancjalizacji jednostek

źródło: comment_KloDqPjcmjE27kpVgI9EuTbCQS4ovtXF.jpg

Pobierz- 1

- 0

@fhrh: ciężko mi odpowiedzieć, na Politechnice mam dostęp do biblioteki i tam wygrzebuję informacje z paru książek naraz i łącze to w całość. Żadna nie nauczyła mnie sama z siebie tego co tu pokazałem - też nie czytałem żadnej od początku do końca. Do tego internet - videotutoriale na YT, stackoverflow-podobne serwisy, gotowe programy...

- 2

Piszę sobie licznik do debouncera przycisku (napisałem sam debouncer w jednym pliku i działał, ale teraz chcę podzielić to na dwa pliki i dwie osobne jednostki: uogólniony licznik i debouncer) i mam problem z instrukcją:

Kod wygląda tak:

http://pastebin.com/UzSgSGPi

Q <= '1' when (clkCounter = target) else '0';Kod wygląda tak:

http://pastebin.com/UzSgSGPi

- 13

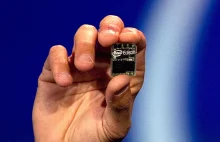

Zaczynamy zabawę z tym czymś zwanym FPGA ( ͡° ͜ʖ ͡°)

#fpga #mikrokontrolery #programowanie #visherdev #elektronika #altera

#fpga #mikrokontrolery #programowanie #visherdev #elektronika #altera

źródło: comment_SakMi2GBHYDnrFr3HZTKymbRGmhQ0ncd.jpg

Pobierz@Visher: co to je, ile kosztowało cebulonów. opisuj postępy, wrzuć linki i w ogóle chwal się nawet jak pomrugasz diodą

40

Intel kupuje Alterę!

Za 16 miliardów dolarów

z- 7

- #

- #

- #

- #

- #

- #